Free Download Mentor Graphics Calibre 2022.38.20 with PDF Documentation | 19.0 Gb

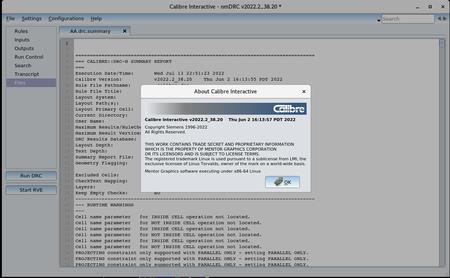

The software developer Siemens EDA (formerly Mentor Graphics) has unveiled Calibre 2022.2.38.20. This Design Solutions delivers a complete IC verification and DFM optimization platform that speeds designs from creation to manufacturing, addressing all sign-off requirements.

Product:Mentor Graphics Calibre

Version:(aoj) 2022.2.38.20 with PDF Documentation *

Supported Architectures:x86_64

Website Home Page :www.mentor.com

Languages Supported:english

System Requirements:Linux **

Size:19.0 Gb

Siemens EDA (formerly Mentor Graphics)is a leader in IC design, verification, and manufacturing. Our tools enable customers to design the innovative ICs that are driving digitalization worldwide, proliferating high-speed wired and 5G communications, cloud computing, autonomous driving, and AI-smarter everything.

Calibre Design Solutionsis the industry leader for IC verification, due to the exceptional performance, accuracy, and reliability of the Calibre nmPlatform. Tight collaboration with foundries, IC design houses, and industry standards organizations ensures Calibre tools continuously provide innovative functionality that meets or exceeds state-of-the-art requirements and delivers real competitive value.

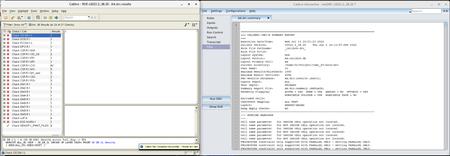

Calibreis one of the most popular toolsthat is widely used by design organizations and foundries. Calibrehas different modules that perform a variety offunctions post-tapeout. Thechallenge ofthe post-tapeout workflow ismaintaining tight control for high waferyield that would lead to a reduction inthe time-to-mask and operation costs. Whilesome of the workloads from modules such asscatter barand bias in the pre-OPC stage arememory intensive, the workloads generated from PM, OPC,and MDP are latency intensive. They rely on the performance of the storage, network,and computeinfrastructure in ordertosupport and complement the speed and quality of Calibre.

Calibre is one of the most commonly usedtools in the silicon on chip (SoC) manufacturing process. This processhandles different parts of the workflow from Calma Graphic Data System (GDSII) to mask flow, providing high wafer yield and reducing the cost of operation. The input files provided from the chip design houses include physical details of SoCsin a GDSIIorOpen Artwork System Interchange Standard (OASIS)format. While Calibreas an application is getting more optimized to reduce the time to mask, the underlying storage infrastructure also plays a significant role on turnaround time (TAT).The infrastructureconsists of network file share storage, the network layer, and the compute farm. NetApp storage is primarily used to store the GDSII/OASIS files and the intellectual property filesin a shared file system accessed by Calibrefrom the compute farm nodes over Network File System(NFSv3).

Design with Calibre

Mentor Graphics Corporation, a Siemens business, is a world leader in electronic hardware and software design solutions, providing products, consulting services, and award-winning support for the world's most successful electronic, semiconductor, and systems companies. Corporate headquarters are located at 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777.

Mentor.Calibre.2022.2.38.20.aoj

Mentor.Calibre.2022.2.PDF.Documentation

Bonus: Mentor.Calibre.2021.1_26.16.aoi

Rapidgator-->Click Link PeepLink Below Here Contains Rapidgator

http://peeplink.in/3ab3551f196e

Uploadgig

http://peeplink.in/c6fe93807e15

NitroFlare

http://peeplink.in/678c9c5f9464

Links are Interchangeable - Single Extraction